The PPG 1020 is known as the stable successor of the 1002 synthesizer. This was achieved by use of a special oscillator architecture that combines digital octave division and a closed-loop approach including a VCO. The VCO covers the whole range(4 keyboard octaves + approx one more for the “digital modulation” feature), but being within a closed loop, it is stabilized to some degree. The details will be topic of a later blog post. For now we only need to know that we need a digital word that determines the octave and a control voltage to drive the VCO to one out of 12 semitones.

Even without the use of a processor (the 1020 does not have a computer of any kind) it would be straight forward: scan the 49 keys, somehow divide the number of the pressed key modulo 12, the result will be the (already digital) octave number, the remainder drives a DAC to generate the CV.

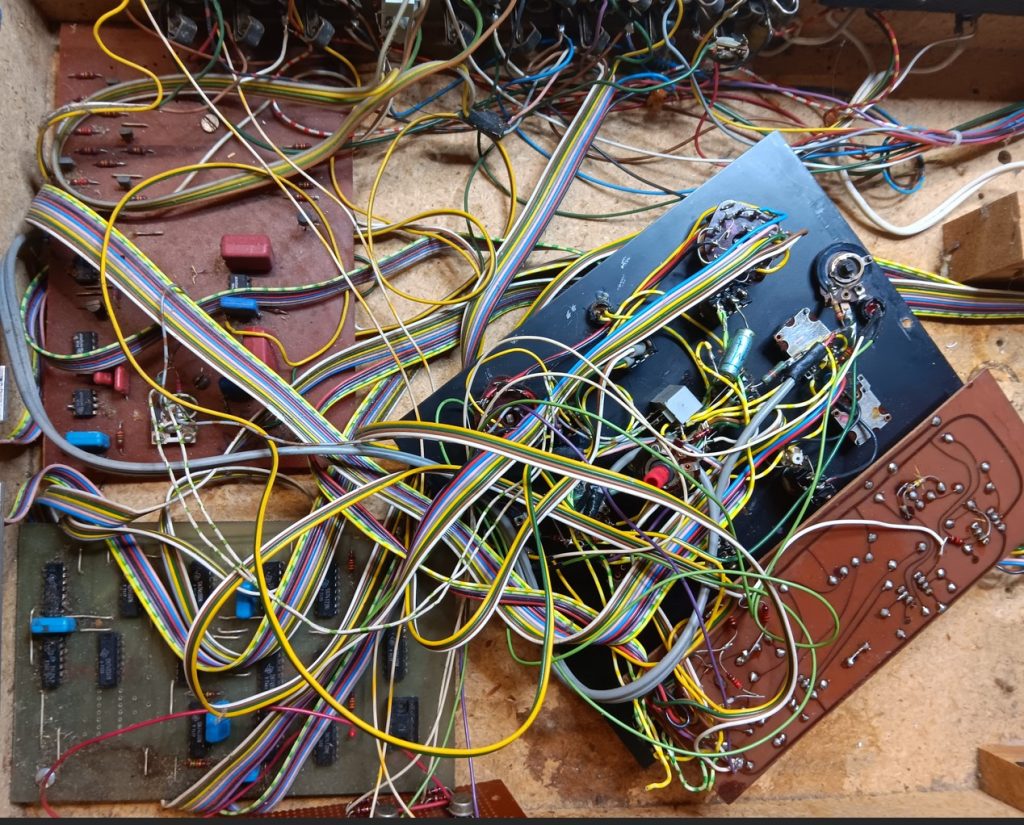

This “somehow” was actually done by using synchronously counting registers – a chain of 2 binary counters, one turning over at 12, the other incrementing whenever the first one turns over, and a chain of shift registers scanning the keys. The first “high” (pressed key) in the serial pulse train from the shift registers will latch the counter outputs in the next cycle, so we have a low-note priority here.

The counters mentioned above drive the octave control word and a digital-to-analog converter built from two 4051 multiplexers and a chain of accordingly weighted resistors. The reference voltage to that chain is generated on the main board and derived from the setting of the tune knob and the pitch bend slider.

For modulation purposes, an offset is digitally imposed. Since the modulation source from the main board is an analog control voltage, analog-to-digital conversion is necessary. A discrete A/D converter was built from a constant current source generating a linear voltage ramp on a capacitor. This slope is than compared with the modulation voltage in order to reset the above mentioned counters, thereby shifting the generated octave control word and the control voltage. With this approach it is possible to modulate the pitch across an octave border, whereas the analog part of the oscillator control would be limited to variation within an octave.

The comparator in this A/D converter is built from discrete transistors, yet integrated into a CA3086. The same circuit, but under processor control, can be found on the analog panel board (ANIN) of the Wave Computer 360!

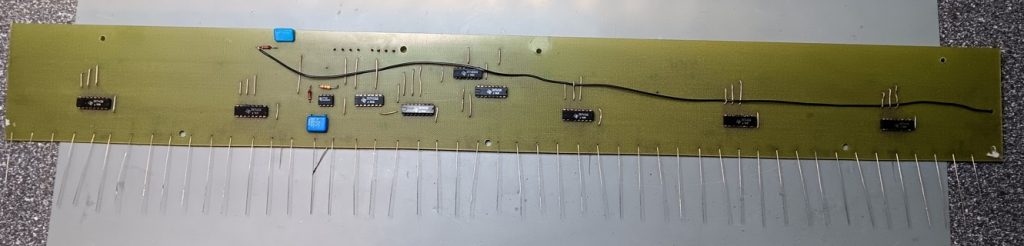

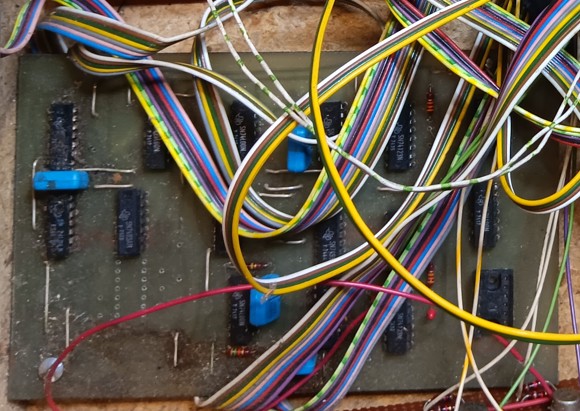

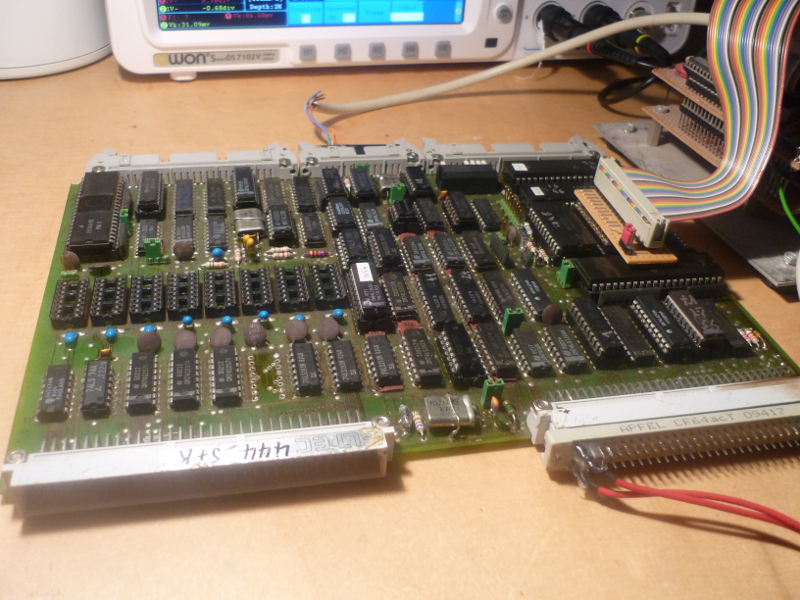

Here’s the component side of the keyboard PCB:

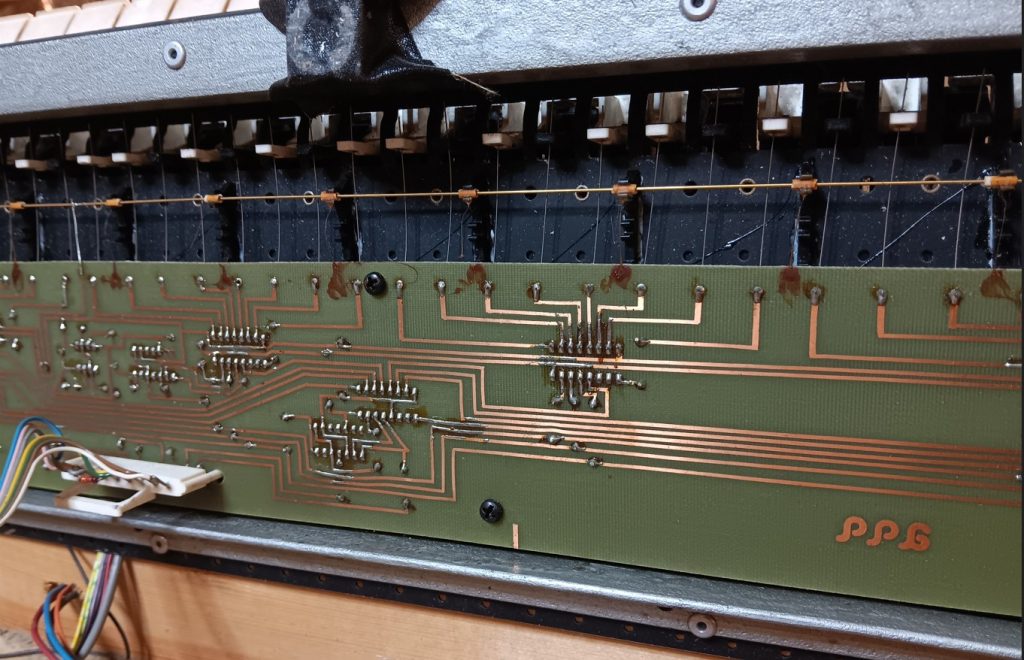

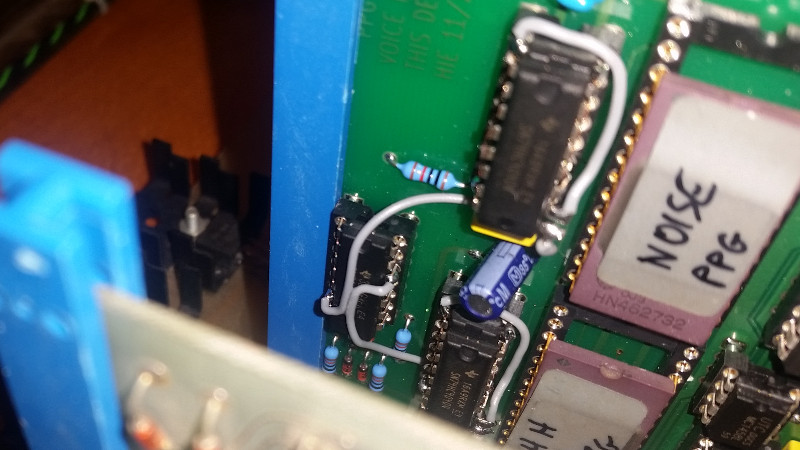

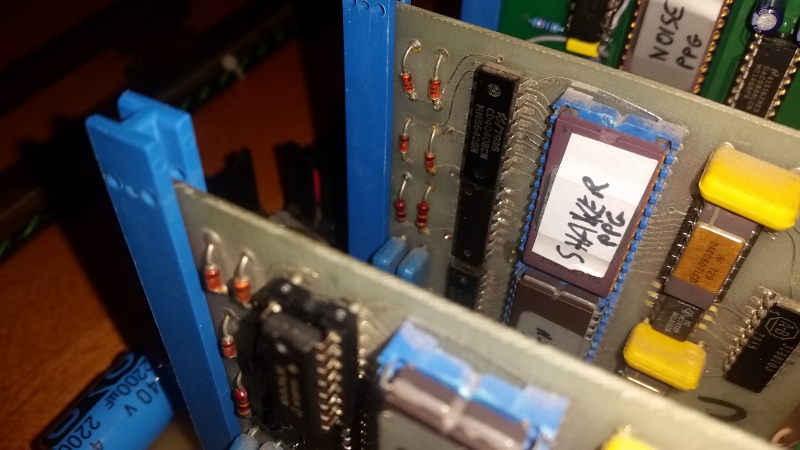

While the copper areas in the right top and middle right are of no electrical use, the long copper stripe on the lower edge is actively driven by a delayed clock signal. One might wonder what the reason for this could be – a view on the solder side and some circuit analysis reveals the secret:

Every key has a 2x1cm big copper area connected to the J-wire on the opposite side. Electrically, each key is capacitively coupled to a delayed clock signal – a signal that is logical “0” whenever the shift registers sample the key lines. This loose coupling is easily overriden by a J-wire touching the bus bar, which is connected to the positive supply voltage by a resistor of just 1k.

The last question about this is: was this only done to eliminate the need for 49 pull down resistors (the shift registers are CMOS devices and would not work properly with open inputs), or were other aspects like debouncing in mind?

A 3.3meg resistor added between one key line and ground suggests that the capacitive pull-down idea did not work 100%.