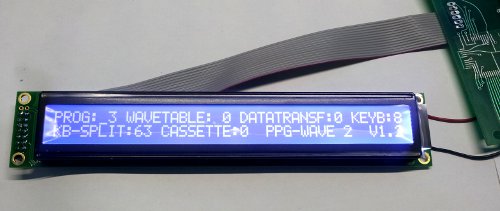

The PPG WAVE2 DRS ADAPTER – demasked

First a short summary of the jacks and switches:

First a short summary of the jacks and switches:

On the left we have 6 phone jacks labelled A to F, one named START/STOP

and a 5pin DIN connector for TAPE SYNC.

Three switches allow to enable a click sound (there’s a small speaker in the DRS box), one to choose between internal or external clock and another to select whether the clock outputs shall be 3 or 4 times the internal timebase.

The phone jacks on the bottom invite the user to feed either a contact-closure or positive voltage trigger signal, the third one labelled INPUT needs to be connected to the trigger in jack on the Wave 2 – there’s no trigger input pin on the 14pin Amphenol connector, only an output!

Before I start with the description of the 5 right side jacks named CL.1 to CL.5 I’d like to tell all those people who can’t wait to hook this adapter to their Wave 2’s not to have too great expectations, or probably learn some 6809 assembly language.

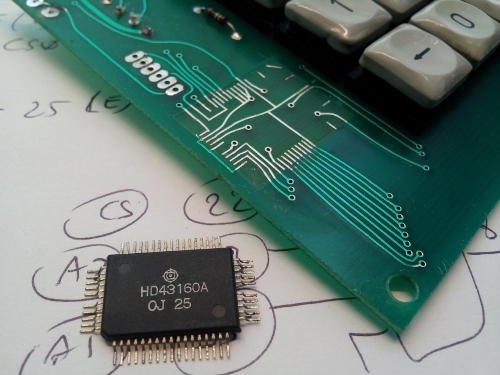

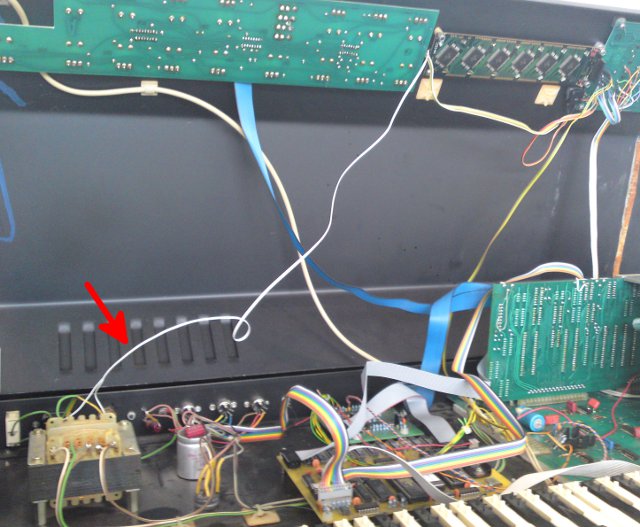

No, let me start with the bad news instead of the clock outputs. The inputs A-F on the left are not connected within the box. The resistor pack which would close the circuit between the jacks and some port pins of the Wave 2’s VIA chip (which are, for those who really want to hack the firmware, the pins PA4..7 and PB0..1) is not fitted and has never been there.

Furthermore, no known firmware for the Wave 2 – and we know three different versions at the time of writing – has a single line of code that communicates with those port pins in any way.

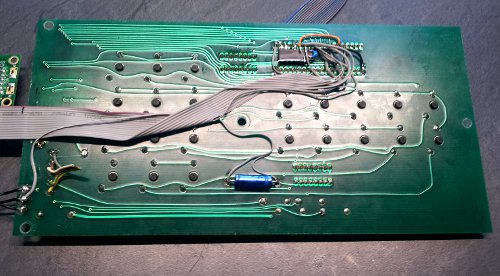

Now let’s have a look at the circuitry that actually could work.

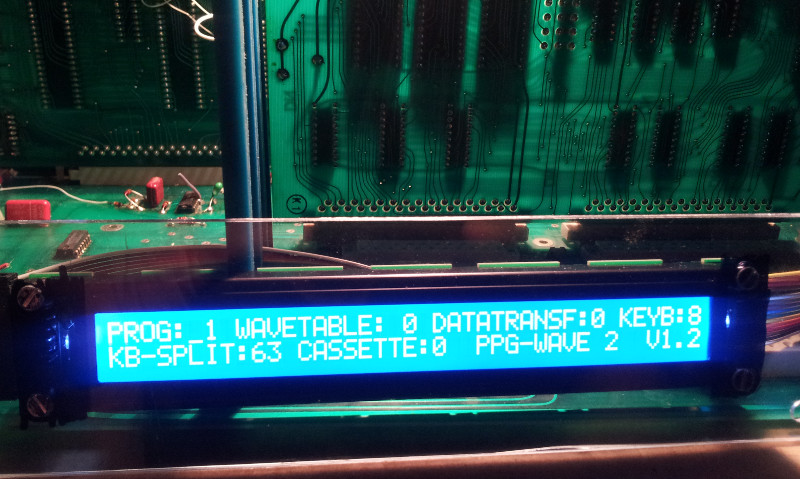

For understanding it is helpful to know that the Wave 2 has a programmable triple timer chip, a Motorola 6840. Timer #3 generates a clock signal that is normally fed to the clock input of Timer #1 through a 10k resistor. This allows to either tap the internal clock, or to override Timer #3’s output to force an external clock to become the clock source of Timer #1 and thereby control the clock for sequencer, arpeggiator and maybe other functions.

This mixed output/input is connected to the DRS box and directly available on the record out pins of the 5pin DIN jack for tape recorder connection. This allows to record the internal clock to a tape or cassette. In addition the clock signal is routed to two frequency dividers: one, dividing by 8, is selected by the clock switch in the x4 position. By using some advanced mathematics, I was able to calculate that the clock signal generated by Timer #3 is 32 times of … something.

For the x3 position of this switch, Wolfgang and his guys made quite some effort so the x3 clock scaling must have been very important. The clock signal is divided by a binary counter that resets itself when reaching a value of 11, but this would be a little bit too slow to reach 3 times the base clock (32/11 is less than 3, q.e.d.), so the counter is additionally reset whenever the counter of the by-8-divider reaches a value of 32. This way a mean frequency of 3 times something with some jitter is achieved.

Whatever the x3/x4 switch selects is buffered and shows up on the jack CL.1 at 5Vpp. CL.2 to CL.5 carry the clock from CL.1 consecutively divided by 2, 4, 8 and 16. That’s all. It’s up to your imagination what you could do with 3 or 4 times the internal sequencer clock. The CL.4 signal, namely 1/2 or 3/8 of the sequencer clock, makes the speaker click unless told not to do so by the CLICK switch.

If you have recorded some signal to a cassette, you would be able to send it back as the sequencer clock through the DRS box.

The playback pins of the DIN jack are followed by a detector (as simple as a CMOS Schmitt trigger) and a buffer which overrides the clock input of Timer #1 when the switch is set to EXTERNAL.

Finally there’s a START/STOP jack. It’ driven by an inverted version of the CA2 pin of the Wave 2’s VIA chip. When the sequencer is stopped, this pin goes high, disabling all the internal circuity of the DRS box – the counters of the frequency dividers are kept in reset state, and all outputs are forced low, including the tape recording output and the clock jacks. The START/STOP output is low in this state. It goes high when CA2 becomes low, which is whenever the sequencer is started.

For those who still want to know everything about this little box, here’s the mapping between VIA pins and jacks:

A -> PB0

B -> PB4

C -> PA7

D -> PA4

E -> PA5

F -> PA6